## MP2672

## Boost Charger with Cell Balance for 2-cell in series Lithium-ion Battery

The Future of Analog IC Technology

#### PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

## DESCRIPTION

The MP2672 is a high-integrated, flexible switch-mode battery charge IC for Lithium-ion battery with 2 cells in series which is used in a wide range of portable applications.

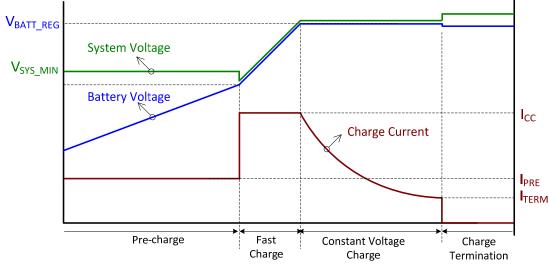

When the input power supply is present, the MP2672 operates in boost mode to charge the battery with 2 cells in series. When the charging is enabled, MP2672 automatically detects the battery voltage and charges the battery in the three phases: pre-charge, constant current charge and constant voltage charge. Other features include charge termination and auto-recharge.

The MP2672 also has narrow voltage DC (NVDC) power structure. When battery is weak, MP2672 regulates the system output at minimum voltage level to power the system instantly and charge battery via battery FET simultaneously.

The MP2672 also has cell-balance function. It will always monitor voltage across each cell and equalize cell voltages once the difference exceeds the mismatch threshold.

The MP2672 has two configuration modes, standalone mode and host-control mode. In standalone mode, the charging parameters can be configured by hardware pins. While in host-control mode, the charging parameter can be configured by l<sup>2</sup>C registers.

The MP2672 has diversified and robust protections. It has thermal regulation loop to decrease the charge current in case the junction temperature exceeds the thermal loop threshold. It also has battery temperature protection compliant to the JEITA standard. Other safety features include input over-voltage protection, battery over-voltage protection, thermal shutdown, battery temperature monitoring, watchdog timer and а programmable back-up timer to prevent prolonged charging of a dead battery.

## **FEATURES**

- 4.0V-to-5.75V Input Operation Voltage

- Up to 14V Sustainable Voltage

- Up to 2A Programmable Charge Current for Battery with 2 cells in Series

- Compatible with Host-control and Standalone Mode

- NVDC Power Path Management

- Programmable Input Voltage Limit

- Programmable Charge Voltage with 0.5% Accuracy

- No External Sense Resistor Required

- Integrated Cell Balancing Circuit for Cell Mismatch

- Preconditioning for Fully Depleted Battery

- Flexible New Charging Cycle Initiation

- Charging Operation Indicator in Standalone

Mode

- Missing Battery Detection in Host-control

Mode

- I<sup>2</sup>C Port for Flexible System Parameter Setting and Status Reporting in Host-control Mode

- Negative Temperature Coefficient Pin for Temperature Monitoring Compliant to JEITA Standard

- Built-in Charging Protection and Programmable Safety Timer

- MOSFET Cycle-by-Cycle Over Current

Protection

- Thermal Regulation and Thermal Shutdown

- 2mmx3mm QFN-18 package

## **APPLICATIONS**

- Portable Hand-held Solutions

- POS Machine

- Blue-tooth Speaker

- E-Cigarette

- General 2-Cell Application

All MPS parts are lead-free, halogen free, and adhere to the RoHS directive. For MPS green status, please visit MPS website under Quality Assurance. "MPS" and "The Future of Analog IC Technology" are Registered Trademarks of Monolithic Power Systems, Inc.

## **TYPICAL APPLICATION**

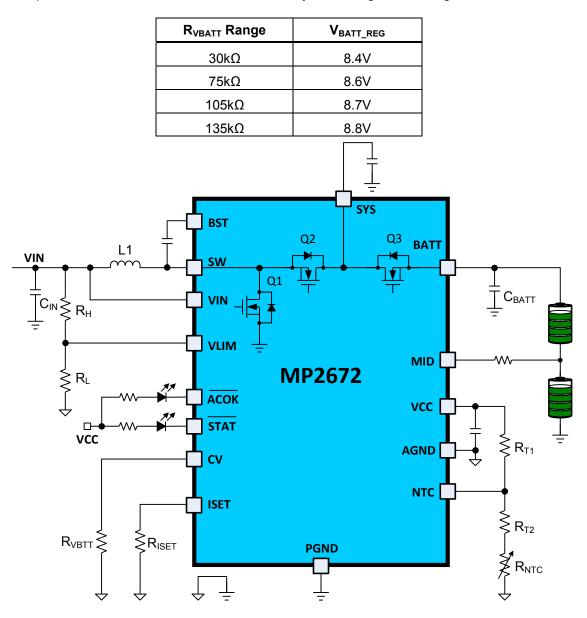

#### Standalone Mode:

Connect CV pin to AGND via a resistor. Set the battery full voltage according to below table.

## **TYPICAL APPLICATION**

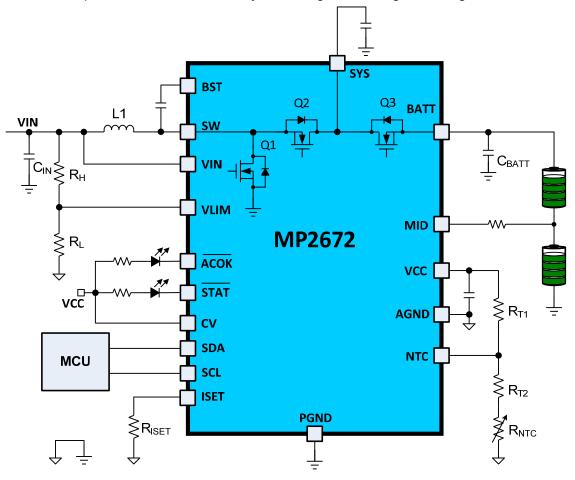

#### Host-control Mode

Connect CV pin to VCC. Set the battery full voltage according to the register.

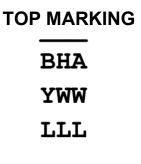

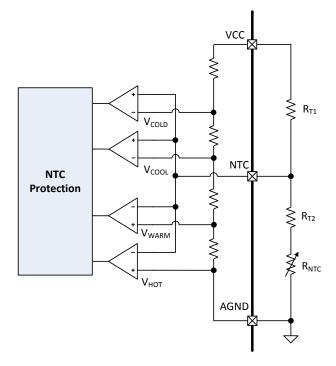

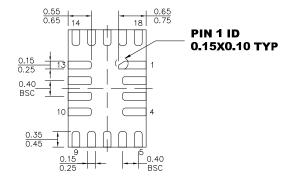

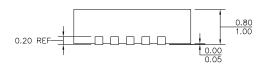

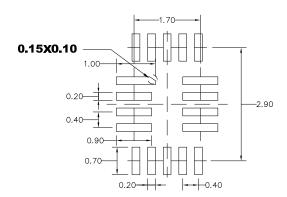

### **ORDERING INFORMATION**

| Part Number*    | Package          | Top Marking |

|-----------------|------------------|-------------|

| MP2672GD-xxxx** | QFN-18 (2mmx3mm) | See Below   |

\*For Tape & Reel, add suffix –Z (e.g. MP2672GD–xxxx-Z)

\*\*"xxxx" is the register setting option. The factory default is "0000". This content can be viewed in the "I<sup>2</sup>C REGISTER MAP" section. For customer options, please contact an MPS FAE to obtain a "xxxx" value.

Y: year code WW: week code BHA: part number LLL: lot number

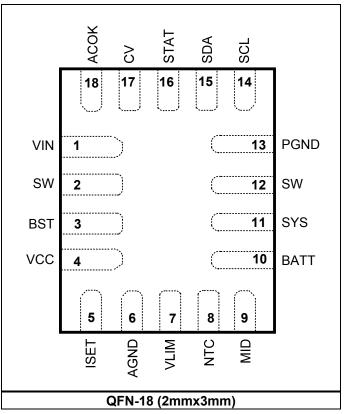

## PACKAGE REFERENCE

## **PIN FUNCTIONS**

| Package<br>Pin # | Name | Туре  | Description                                                                                                                                                                              |

|------------------|------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                | VIN  | I     | Input voltage sense pin and power supply for VCC LDO.                                                                                                                                    |

| 2, 12            | SW   | Power | Switching Node. Middle point of the high-side and low-side FET of the boost.                                                                                                             |

| 3                | BST  | Power | Bootstrap. Connect a bootstrap capacitor between BST and SW to provide a floating supply to the high-side FET driver.                                                                    |

| 4                | VCC  | Power | Internal LDO output pin. Bypass a 2.2µF ceramic capacitor from this pin to AGND. Recommend pull no more than 30mA current from this pin.                                                 |

| 5                | ISET | I     | Connect an external resistor to GND to program the charge current, which also limit the maximum charge current in Host-control mode.                                                     |

| 6                | AGND | I/O   | Analog ground.                                                                                                                                                                           |

| 7                | VLIM | I     | Input Voltage Limit feedback pin. Connect a resistive divider from VIN to AGND to program the minimum input voltage limit threshold.                                                     |

| 8                | NTC  | I     | Battery Temperature Sense Input. See NTC protection section.                                                                                                                             |

| 9                | MID  | I/O   | Middle point of the high-side and low-side cell. Used to measure the voltage and provide balance path for each cell.                                                                     |

| 10               | BATT | Power | Battery positive terminal. Connect a $22\mu F$ capacitor from BATT to PGND as close as possible to the IC.                                                                               |

| 11               | SYS  | Power | System Output. Connect a $2 \times 22 \mu F$ capacitor from SYS to PGND as close as possible to the IC.                                                                                  |

| 13               | PGND | Power | Power ground.                                                                                                                                                                            |

| 14               | SCL  | I/O   | I <sup>2</sup> C Interface Clock Pin. Not valid if CV pin is connected to VCC.                                                                                                           |

| 15               | SDA  | I/O   | I <sup>2</sup> C Interface Data Pin. Not valid if CV pin is connected to VCC.                                                                                                            |

| 16               | STAT | I/O   | Open-drain indicator for charging operation. Also can be used as INT in Host-control mode.                                                                                               |

| 17               | CV   | I     | Pull CV to VCC to configure IC to host-control mode. Connect an external resistor to GND to configure IC to standalone mode and program the battery full voltage via the resistor value. |

| 18               | ACOK | 0     | Open-drain Input Supply Indicator. It's an open-drain output. It is pulled to Low when input voltage is higher than $V_{\rm IN\ UVLO}$ and $V_{\rm IN\ OVLO}.$                           |

## ABSOLUTE MAXIMUM RATINGS (1)

|                                                   | -                 |

|---------------------------------------------------|-------------------|

| BATT0.3V to +                                     | ⊦14V              |

| SW,0.3V (-2V for 50ns) to +                       | ⊦14V              |

| SYS0.3V to +                                      | ⊦14V              |

| MID, VIN0.3V to +                                 | ⊦12V              |

| BST to SW0.3V to                                  | +5V               |

| All Other Pins to GND0.3V to                      | +5V               |

| Continuous Power Dissipation(T <sub>A</sub> =+25° | C) <sup>(2)</sup> |

|                                                   | 78W               |

| Junction Temperature15                            |                   |

| Lead Temperature (Solder)26                       | 30°C              |

| Storage Temperature65°C to +15                    | 50°C              |

|                                                   | (0)               |

## Recommended Operating Conditions <sup>(3)</sup>

| VIN to GND                | 4V to 5.75V      |

|---------------------------|------------------|

| BATT to GND               | up to 9V         |

| I <sub>CHG</sub>          | up to 2A         |

| I <sub>DSCHG</sub>        | Up to 3A         |

| I <sub>SYS</sub>          | Up to 2.5A       |

| Operating Junct. Temp. (T | J)40°C to +125°C |

#### Thermal Resistance <sup>(4)</sup> $\theta_{JA}$ $\theta_{JC}$

QFN2x3 ...... 70 ..... 15....°C/W

#### Notes:

- 1) Exceeding these ratings may damage the device.

- 2) The maximum allowable power dissipation is a function of the maximum junction temperature T<sub>J</sub> (MAX), the junction-toambient thermal resistance  $\theta_{JA}$ , and the ambient temperature T<sub>A</sub>. The maximum allowable continuous power dissipation at any ambient temperature is calculated by P<sub>D</sub> (MAX) = (T<sub>J</sub> (MAX)-T<sub>A</sub>)/ $\theta_{JA}$ . Exceeding the maximum allowable power dissipation will cause excessive die temperature, and the regulator will go into thermal shutdown. Internal thermal shutdown circuitry protects the device from permanent damage.

- The device is not guaranteed to function outside of its operating conditions.

- 4) Measured on JESD51-7, 4-layer PCB.

## **ELECTRICAL CHARACTERISTICS**

$V_{IN}$  = 5V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter $V_{\rm IN} = 5V$ , $T_{\rm A} = 25$ C, unless C                           | Symbol                       | Condition                                                  | Min  | Тур                                     | Мах  | Units |

|--------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------------|------|-----------------------------------------|------|-------|

| Input Power Characteristics                                                          | 5                            |                                                            |      | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |      |       |

| Input Over-voltage Lock-out<br>Threshold                                             | V <sub>IN_OVLO</sub>         | $V_{IN}$ rising                                            | 5.75 | 6.0                                     | 6.25 | V     |

| Input Over-Voltage Lock-out<br>Threshold Hysteresis                                  |                              |                                                            |      | 150                                     |      | mV    |

| Input Under-voltage Lock-out<br>Threshold                                            | $V_{\text{IN}\_\text{UVLO}}$ | V <sub>IN</sub> falling                                    | 3.35 | 3.55                                    | 3.75 | V     |

| Input Under-voltage Lock-out<br>Threshold Hysteresis                                 |                              |                                                            |      | 150                                     |      | mV    |

| Boost Converter                                                                      |                              |                                                            |      |                                         |      |       |

| Input Quiescent Current                                                              | I <sub>IN_Q</sub>            | Battery and system are float,<br>Charging is enabled       |      |                                         | 2.5  | mA    |

| VCC LDO Output                                                                       | V <sub>VCC</sub>             | V <sub>IN</sub> =5V, I <sub>VCC</sub> =20mA                | TBD  | 3.6                                     | TBD  | V     |

| Low Side NFET On Resistance                                                          | $R_{ON_Q1}$                  |                                                            |      | 60                                      | 80   | mΩ    |

| High Side NFET On Resistance                                                         | $R_{ON_{Q2}}$                |                                                            |      | 30                                      | 40   | mΩ    |

| Peak Current Limit for Low-<br>side NFET                                             | $I_{LS_{PK}}$                | Step-up Mode                                               | 6    | 7                                       |      | А     |

| Valley Current Limit for High-<br>side NFET                                          | I <sub>HS_VL</sub>           | Step-up Mode                                               | 5    | 6                                       |      | А     |

| Operating Frequency                                                                  | $F_{SW}$                     | REG07 Bit[7]=1                                             | TBD  | 1200                                    | TBD  | kHz   |

|                                                                                      |                              | REG00Bit[3:1]=000,<br>REG00Bit[0]=0, V <sub>BATT</sub> =5V | TBD  | 6.2                                     | TBD  |       |

| System Regulation Minimum<br>Voltage<br>(V <sub>BATT PRE</sub> +V <sub>TRACK</sub> ) | $V_{\text{SYS}\_\text{MIN}}$ | REG00Bit[3:1]=100,<br>REG00Bit[0]=0, V <sub>BATT</sub> =5V | TBD  | 6.6                                     | TBD  | V     |

| (VBATI_PRE VIRACK)                                                                   |                              | REG00Bit[3:1]=111<br>REG00Bit[0]=1, V <sub>BATT</sub> =5V  | TBD  | 7                                       | TBD  |       |

| Battery Track Regulation                                                             | V <sub>TRACK</sub>           | REG00 Bit[0]=0                                             |      | 200                                     |      | mV    |

| Voltage                                                                              | V TRACK                      | REG00 Bit[0]=1                                             |      | 300                                     |      | IIIV  |

| Battery Charger                                                                      |                              |                                                            |      |                                         |      |       |

|                                                                                      |                              | REG00 Bit [3:1]=000                                        | TBD  | 6.0                                     | TBD  |       |

| Pre Charge Threshold                                                                 | $V_{\text{BATT}_{PRE}}$      | REG00 Bit [3:1]=100                                        | TBD  | 6.4                                     | TBD  | V     |

|                                                                                      |                              | REG00 Bit [3:1]=111                                        | TBD  | 6.7                                     | TBD  |       |

| Pre Charge Threshold<br>Hysteresis                                                   |                              | V <sub>BATT</sub> falling                                  |      | 175                                     |      | mV    |

| Pre Charge Current                                                                   | I <sub>PRE</sub>             |                                                            | 80   | 100                                     | 120  | mA    |

## ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                            | Symbol                        | Condition                                                                                                                                                                                                                                                                                                                                                                              | Min  | Тур | Мах  | Units |

|------------------------------------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| Fast Charge Current                                  |                               | Host-control mode,<br>REG01Bit[3:0]=1111,<br>$R_{ISET}=24k\Omega$ ,<br>Standalone mode,<br>$R_{ISET}=24k\Omega$                                                                                                                                                                                                                                                                        | 0.4  | 0.5 | 0.6  | A     |

| Past Gharge Guitent                                  | I <sub>CC</sub>               | Host-control mode,<br>REG01Bit[3:0]=1111,<br>$R_{ISET} = 6k\Omega$ ,<br>or in standalone mode,<br>$R_{ISET} = 6k\Omega$                                                                                                                                                                                                                                                                | 1.8  | 2   | 2.2  | A     |

| Termination Charge Current                           | I                             | As the percentage of $I_{CC}$                                                                                                                                                                                                                                                                                                                                                          | 5    | 10  | 15   | %     |

| Termination Charge Current                           | I <sub>TERM</sub>             | lf 10%*I <sub>CC</sub> < 150mA                                                                                                                                                                                                                                                                                                                                                         | 120  | 150 | 180  | mA    |

| Input Minimum Voltage<br>Regulation Reference        | V <sub>IN_MIN_RE</sub>        |                                                                                                                                                                                                                                                                                                                                                                                        | 1.18 | 1.2 | 1.22 | V     |

|                                                      |                               | V <sub>BATT_REG</sub> =8.3V,<br>Host-control mode,<br>REG00[7:5]=000,                                                                                                                                                                                                                                                                                                                  |      |     | 0.5  |       |

| Battery Charge Voltage<br>Regulation                 | V <sub>BATT_REG</sub><br>_acc | $\label{eq:VBATT_REG} \begin{array}{l} V_{\text{BATT_REG}} = 8.4 V, \\ \text{Host-control mode,} \\ \text{REG00[7:5]=001,} \\ \text{/Standalone mode,} \\ \text{R}_{\text{VBATT}} = 30 k \Omega \\ \hline \\ V_{\text{BATT_REG}} = 8.8 V, \\ \text{Host-control mode,} \\ \text{REG00[7:5]=101,} \\ \text{/Standalone mode,} \\ \text{R}_{\text{VBATT}} = 135 k \Omega \\ \end{array}$ | -0.5 |     |      | %     |

|                                                      |                               | V <sub>BATT_REG</sub> =9.0V,<br>Host-control mode,<br>REG00[7:5]=111                                                                                                                                                                                                                                                                                                                   |      |     |      |       |

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ | $V_{RECH}$                    |                                                                                                                                                                                                                                                                                                                                                                                        |      | 400 |      | mV    |

| Battery Over Voltage Protection Threshold            | $V_{BATT_OVP}$                | As the percentage of the $V_{BATT REG}$                                                                                                                                                                                                                                                                                                                                                | 102  | 104 | 105  | %     |

| Battery Over Voltage<br>Protection Hysteresis        |                               | As the percentage of the $V_{BATT REG}$                                                                                                                                                                                                                                                                                                                                                |      | 1   |      | %     |

| SYS to BATT NFET On Resistance                       | R <sub>ON_Q3</sub>            |                                                                                                                                                                                                                                                                                                                                                                                        |      | 30  | 40   | mΩ    |

| Battery Quiescent Current                            | I <sub>BATT_Q</sub>           | V <sub>IN</sub> <v<sub>IN_UVLO, V<sub>BATT</sub>=8.4V,<br/>System no load</v<sub>                                                                                                                                                                                                                                                                                                      |      | 30  |      | μA    |

| ACOK, STAT, pin output low voltage                   |                               | Sinking 1.5mA                                                                                                                                                                                                                                                                                                                                                                          |      |     | 400  | mV    |

| ACOK, STAT, pin leakage current                      |                               | Connected to 5V                                                                                                                                                                                                                                                                                                                                                                        |      |     | 1    | μA    |

## ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                           | Symbol                 | Condition                                      | Min  | Тур  | Max  | Units |

|-----------------------------------------------------|------------------------|------------------------------------------------|------|------|------|-------|

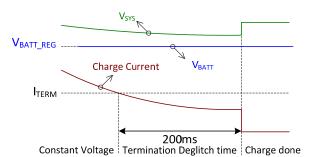

| Termination Deglitch Time                           | t <sub>TERM DGL</sub>  |                                                |      | 200  |      | ms    |

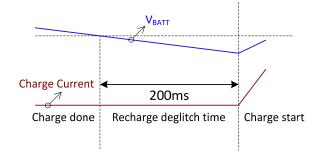

| Recharge Deglitch Time                              | t <sub>RECH DGL</sub>  |                                                |      | 200  |      | ms    |

| <b>Battery Temperature Monitor</b>                  | ing (JEITA             | )                                              |      |      |      |       |

| NTC Low Temp Rising<br>Threshold                    | V <sub>COLD</sub>      | As percentage of $V_{cc}$                      | 68.8 | 70.8 | 72.8 | %     |

| NTC Low Temp Rising<br>Threshold Hysteresis         |                        | As percentage of $V_{\text{CC}}$               |      | 2    |      | %     |

| NTC Cool Temp Rising<br>Threshold                   | V <sub>COOL</sub>      | As percentage of $V_{CC}$                      | 60.9 | 62.9 | 64.9 | %     |

| NTC Cool Temp Rising<br>Threshold Hysteresis        |                        | As percentage of $V_{cc}$                      |      | 2    |      | %     |

| NTC Warm Temp Falling<br>Threshold                  | V <sub>WARM</sub>      | As percentage of $V_{cc}$                      | 38.3 | 40.3 | 42.3 | %     |

| NTC Warm Temp Falling<br>Threshold Hysteresis       |                        | As percentage of $V_{CC}$                      |      | 2    |      | %     |

| NTC Hot Temp Falling<br>Threshold                   | V <sub>HOT</sub>       | As percentage of $V_{\text{CC}}$               | 32.5 | 34.5 | 36.5 | %     |

| NTC Hot Temp Falling<br>Threshold Hysteresis        |                        | As percentage of $V_{CC}$                      |      | 2    |      | %     |

| Thermal Regulation and Prot                         | ection                 |                                                |      |      |      |       |

| Junction Temperature<br>Regulation                  | $T_{J\_REG}$           |                                                |      | 120  |      | °C    |

| Thermal Shutdown<br>Temperature <sup>(1)</sup>      | $T_{J_SHDN}$           | Rising Threshold                               |      | 150  |      | °C    |

| Thermal Shutdown<br>Hysteresis <sup>(1)</sup>       |                        |                                                |      | 20   |      | °C    |

| Cell Balance Function                               |                        |                                                |      |      |      |       |

| Internal Balance FET On                             | R <sub>ON BHS</sub>    |                                                |      | 2    |      | Ω     |

| Resistance                                          | R <sub>on bls</sub>    |                                                |      | 2    |      | Ω     |

| Cell Balance Start Voltage<br>Threshold             | V <sub>CELL_BAL</sub>  | l <sup>2</sup> C programmable, REG01<br>Bit6=1 | 3.6  | 3.7  | 3.8  | V     |

| Cell Voltage High to Low Cell<br>Mismatch Threshold | V <sub>CELL_DIFF</sub> |                                                | 40   | 50   | 60   | mV    |

| Cell Voltage Low to High Cell<br>Mismatch Threshold | V <sub>CELL_DIFF</sub> |                                                | 40   | 50   | 60   | mV    |

| Balance Threshold Hysteresis                        |                        |                                                |      | 30   |      | mV    |

## ELECTRICAL CHARACTERISTICS (continued)

$V_{IN}$  = 5V,  $T_A$  = 25°C, unless otherwise noted.

| Parameter                                | Symbol           | Condition                                           | Min | Тур | Max | Units |

|------------------------------------------|------------------|-----------------------------------------------------|-----|-----|-----|-------|

| I <sup>2</sup> C Communication Interface |                  |                                                     |     |     |     |       |

| Input High Threshold Level               | V <sub>IH</sub>  | V <sub>PULL UP</sub> = 1.8V                         | 1.3 |     |     | V     |

| Input Low Threshold Level                | V <sub>IL</sub>  | V <sub>PULL UP</sub> = 1.8V                         |     |     | 0.4 | V     |

| Output Low Threshold Level               | V <sub>OL</sub>  | I <sub>SINK</sub> = 5mA                             |     |     | 0.4 | V     |

| I <sup>2</sup> C Clock Frequency         | F <sub>SCL</sub> |                                                     |     |     | 400 | kHz   |

| Timing Characteristic                    | •                |                                                     | •   | •   | •   | •     |

| Clock Frequency                          | F <sub>CLK</sub> |                                                     |     | 130 |     | kHz   |

| Watchdog Timer                           | t <sub>WTD</sub> | REG02 [5:4]=01                                      |     | 40  |     | S     |

| Safety Charge Timer                      | t <sub>TMR</sub> | I <sup>2</sup> C programmable,<br>REG02 Bit[2:1]=11 |     | 20  |     | Hours |

Notes:

5) Guaranteed by design.

## **TYPICAL PERFORMANCE CHARACTERISTICS**

$V_{IN}$  = 5V,  $T_A$  = 25°C, unless otherwise noted.

<u>=</u>

Insert

#### Performance Curve

Provide Source File (Excel Data & Chart) (Format > Picture > Layout > In Front of Text) Shift-Scale > Alt-Move

## **TYPICAL PERFORMANCE CHARACTERISTICS** (continued)

$V_{IN}$  = 5V,  $T_A$  = 25°C, unless otherwise noted.

Insert

#### Performance Curve

Provide Source File (Excel Data & Chart) (Format > Picture > Layout > In Front of Text) Shift-Scale > Alt-Move

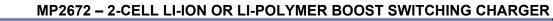

## FUNCTIONAL BLOCK DIAGRAM

Figure 1 Functional Block Diagram

## **OPERATION**

The MP2672 is a highly integrated switch-mode battery charger to charge Lithium-ion battery with 2 cells in series from 5V input power supply, which could be adapter or USB input.

Host-control Mode and Standalone Mode MP2672 can operate in either Host-control mode or standalone mode. After input power on, MP2672 checks CV status first.

- If CV is pulled up to logic high, MP2672 will work in host-control mode.

- If CV is connected to ground through a resistor, MP2672 will work in standalone mode.

In host-control mode, charging parameters can be programmable by  $I^2C$  registers. In standalone mode,  $V_{BATT\_REG}$  and  $I_{CC}$  can be set by external analog pin.

Table 1: Host-control Mode and Standalone

Mode

| CV pin                        | Mode             | $V_{BATT_REG}$                   | I <sub>cc</sub>                         |

|-------------------------------|------------------|----------------------------------|-----------------------------------------|

| Connect<br>resistor<br>to GND | Standalone       | Set by CV<br>resistor            | Set by<br>ISET<br>resistor              |

| Pull up<br>to VCC             | Host-<br>control | Set by I <sup>2</sup> C register | Set by<br>I <sup>2</sup> C<br>register* |

\*Note: Maximum charge current is limited by ISET setting.

#### Internal Power Supply

The VCC LDO is powered by input power supply and it is used to power the internal circuit and MOSFET driver. When the input is absent, the VCC LDO will be off. An external capacitor is required to be connected from VCC pin to GND. The VCC output is regulated at 3.6V typically when  $V_{IN}$  is 5V. When the VIN is lower than 3.6V, the LDO enters into dropout state and LDO FET is fully turned on. VCC output is not able to carry more than 20mA current load.

#### Input Voltage vs. System Voltage Limitation

To avoid the MP2672 entering the open-loop operation due to the minimum on time of low-side FET. The boost converter will turn off when  $V_{SYS} < 1.1 \text{xV}_{IN}$ , it will restart and check the input

voltage and system voltage again. And the boost will turn off again after around 1ms soft-start time if  $V_{SYS}$  is still lower than  $1.1 \times V_{IN}$ .

As a result it is recommended to choose  $V_{BATT\_PRE}$  and  $V_{TRACK}$  to ensure the minimum output voltage of boost is above the 1.1x the maximum DC input voltage.

#### Input Power Start-up

When input voltage is lower than  $V_{IN\_UVLO}$ , SYS is powered by the battery via the Q3, which is fully turned on at this time. When input power is connected, the Q3 will quit fully on mode and enter ideal diode mode when  $V_{IN}$  is higher than  $V_{IN\_UVLO}$ . At the same time the boost starts up with soft-start of the system voltage loop. When the system voltage rises around 20mV higher than the battery voltage the Q3 will be turned off for a while and turn on again with soft-start of charge current after system voltage soft-start completes.

#### **NVDC Power Structure**

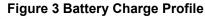

The MP2672 employs the Narrow VDC (NVDC) power structure which is composed of a frondend boost converter and a rear-end battery FET between SYS and BATT pin. By doing this it allows the separate control between the system and the battery. The system is given the priority to start up even with a deeply-discharged or missing battery. So when the input power is available even with a depleted battery, the system voltage is regulated at the minimum system voltage  $V_{SYS\_MIN}$  which is set by I<sup>2</sup>C register REG00 Bit [3:1] and REG00 Bit [0].

As shown in Figure 2, for the system voltage control,

- (1) When the battery voltage is lower than  $V_{BATT\_PRE}$ , the system voltage is regulated at  $V_{SYS\_MIN} = V_{BATT\_PRE}+V_{TRACK}$  and the battery FET works linearly to charge the battery with pre-charge current.

- (2) When the battery voltage is above the  $V_{BATT_PRE}$ , the battery FET is fully turned on, the system voltage is always  $I_{CHG} \times R_{ON_Q3}$  higher than the battery voltage. Once the battery charging is completed, the system output ( $V_{SYS}$ ) is regulated to  $V_{BATT} + V_{TRACK}$ .

(3) When charging is disabled, the  $V_{\text{SYS}}$  is also regulated to  $V_{\text{TRACK}}$  higher than real battery voltage.

Figure 2 V<sub>SYS</sub> Variation with V<sub>BATT</sub>

#### **Battery Charge Profile**

As shown in Figure 2, the MP2672 provides three main charging phases: pre-charge, constant-current charge and constant-voltage charge.

#### Phase 1 (Pre-charge)

When the battery voltage is lower than the  $V_{BATT_PRE}$ , the MP2672 regulates the system voltage at  $V_{SYS\_MIN}$  and apply a safely precharge current  $I_{PRE}$  to the deeply depleted battery until the battery voltage reaches precharge to fast charge threshold  $V_{BATT\_PRE}$ . If  $V_{BATT\_PRE}$  is not reached before pre-charge timer (30 mins) expires, the charge cycle is ceased and a corresponding timeout fault signal is asserted.

Phase 2 (Constant-current charge)

When the battery voltage exceeds  $V_{BATT_PRE}$ , the MP2672 stops the pre-charge phase and enters into fast charge phase. The fast charge current can be programmable via ISET pin in standalone mode or I<sup>2</sup>C register in host mode.

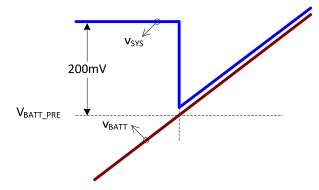

#### Phase 3 (Constant-voltage charge)

As depicted in Figure 4, when the battery voltage rises to the battery regulation voltage  $V_{BATT_{REG}}$ , the charge current begins to decrease. The charge cycle is considered as completed when CV loop dominated and the charge current drops below the charge termination current threshold for 200ms deglitch time. Also a 200ms deglitch time is designed for starting each charge cycle, after 200ms expires the charge full signal will be allowed to assert if termination condition are met.

(a) Force Charge Time

#### (b) Termination Deglitch Time

#### Figure 4 Force Charge Time and Termination Deglitch Time

If I<sub>TERM</sub> is not reached before the safety charge timer expires (see Safety Timer section), the charge cycle is ceased and corresponding timeout fault signal is asserted

A new charge cycle starts when the following conditions are valid:

- The input power is re-plugged

- Auto-recharge

- No thermistor fault at NTC pin.

- No safety timer fault.

- No battery over voltage.

The charge termination can be disabled manually by pulling NTC pin up to VCC.

#### **Automatic Recharge**

As shown in Figure 5, when the battery is charged full and the charging is terminated, the battery may be discharged for the system consumption or self-discharge. The MP2672 automatically starts another new charging cycle without the requirement of manually re-starting a charging cycle when battery voltage drops below the recharge threshold for 200ms.

In case the battery is not expected to be charged frequently during high SOC condition, the MP2672 has an OTP option to disable charging when input power on and battery voltage is higher than recharge voltage threshold. The charging will be enabled till the battery voltage decreases below the recharge threshold.

#### **Battery Full Voltage Setting**

The MP2672 has a CV pin to program the battery regulation voltage.

When CV pin is pulled up to VCC, MP2672 operates in host-control mode. The battery regulation voltage is programmed through l<sup>2</sup>C.

When CV pin is connected to AGND via a resistor, MP2672 operates in standalone mode. The battery regulation voltage is set according to below table.

Table 2: V<sub>BATT\_REG</sub> VS R<sub>VBATT</sub> Resistor

| <b>Resistor Range</b> | V <sub>BATT_REG</sub> |

|-----------------------|-----------------------|

| 30kΩ                  | 8.4V                  |

| 75kΩ                  | 8.6V                  |

| 105kΩ                 | 8.7V                  |

| 135kΩ                 | 8.8V                  |

#### **Charge Current Setting**

In standalone mode, the charge current is programmable via ISET pin. The setting formula is shown as below.

$$I_{cc} = \frac{12k\Omega}{R_{ISET}}(A)$$

(1)

In host mode, the charge current can be programmed via REG01H Bit [3:0] together with  $R_{ISET}$ . The  $R_{ISET}$  determines the full scale value of the register, for example

If  $R_{\text{ISET}}$  is  $6k\Omega$ , REG01H Bit [3:0] programmable range is 500mA to 2000mA with 100mA per step.

If  $R_{ISET}$  is 24k $\Omega$ , REG01G Bit [3:0] programmable range is 125mA to 500mA with 25mA per step.

$R_{ISET}$  is recommended to be within  $6k\Omega - 24k\Omega$ .

#### Minimum Input Voltage Limit

To avoid overloading the adapter, the MP2672 has the input voltage based power management by continuously monitoring the

input voltage. When the minimum input voltage limit is reach the charge current will be reduced to prevent the input voltage from dropping further. The minimum input voltage limit can be programmable by resistive divider at VLIM pin.

The internal reference of the input voltage loop is 1.2V, and the minimum input voltage limit can be set as below formula,

$$V_{\text{IN}_{\text{MIN}}} = 1.2 \times \frac{R_{\text{H}} + R_{\text{L}}}{R_{\text{I}}}$$

(2)

# Battery Supplement Mode and Ideal Diode Mode

As mentioned in last section, when minimum input voltage limit is hit, the charge current is reduced to keep the input voltage not dropping further. But when the charge current is reduce to zero and the input source is still overloaded due to heavy system load, the system voltage will continued dropping. Once the system voltage falls below the battery voltage, the MP2672 enters battery supplement mode. The battery starts to supplement the system load together with boost converter. During the supplement mode, the battery FET operates as an ideal diode.

When the system voltage falls 30 mV below the battery voltage, the battery FET turns on and its

source to drain voltage is regulated at 24mV. As the battery discharge current goes higher the ideal diode loop will be saturated and the battery FET will be fully turned on. The source to drain voltage will be discharge current times the on resistance of battery FET.

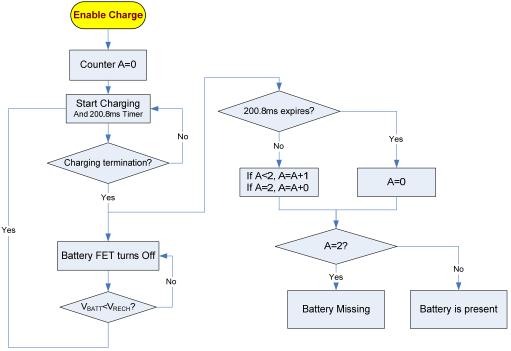

#### **Battery Missing Detection**

The MP2672 is capable of detecting whether a battery is connected or not. The following conditions initiate battery missing detection:

- Charging is enabled.

- Auto-recharge is triggered.

- Recovery from any Faults

If battery absent is detected, Blinking at 1Hz indicates at STAT pin, BATTFLOAT\_STAT is set 1 in host-control mode. Figure 6 shows the battery missing detection flow chart.

#### **Battery Over-Voltage Protection**

The MP2672 is designed with a built-in battery over voltage protection threshold, which is 104% of the  $V_{BATT_{REG}}$ . When the battery over voltage event occurs, the MP2672 turns off the battery FET (Q3) and suspends the charging. At this time the boost converter keeps operating and

#### **Figure 6 Battery Missing Detection Flow chart**

system voltage tracks the battery voltage with additional  $V_{\text{TRACK}}$ .

MP2672 also has a MID pin to monitor each cell voltage. If any one of the cell voltages exceeds 104% of  $V_{BATT_{REG}}/2$ , MP2672 also stop charging the battery.

#### Safety Timer

The MP2672 provides both pre-charge and fast charge cycle safety timer to avoid extended charging cycle due to abnormal battery conditions. The safety timer for pre-charge is 30 minutes when battery is lower than  $V_{BATT_PRE}$ . The fast charge cycle safety timer starts when the battery enters fast charge phase. The fast charge safety timer can be programmed by  $I^2C$ . The safety timer feature can also be disabled via  $I^2C$ .

The safety timer is reset at the beginning of a new charging cycle. Also it can be reset by writing 0 and 1 sequentially to the REG00 Bit4. The following actions restart the safety timer:

- A new charge cycle has begun.

- Write REG00 Bit4 from 0 to 1 (charge enable)

- Write REG02 Bit[2:1] from 00 to 01/10/11 (safety timer enable)

- Write REG02 Bit3 from 0 to 1 (software reset)

The timer is suspended during the conditions below:

• NTC hot or cold fault

In the event of the NTC hot and cold fault, the charging timer will be suspended. Once the NTC fault is removed, the timer will continue to count from the value before NTC fault.

If the input voltage regulation, or thermal regulation threshold is reached, the rest of the timer will be doubled if REG02 Bit0 is set to 1. Once the events above quit, the rest of the timer returns to the original setting.

#### Watchdog Timer

When MP2672 operates in host-control mode, a watchdog timer is provided to reset all the registers to default value if the watchdog timer is not reset periodically. By doing this the register value of MP2672 will go back to default when no action on  $I^2C$  bus for a certain time.

The watchdog timer duration can be programmable and disabled through register.

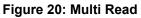

#### NTC (Negative Temperature Coefficient) Thermistor

"Thermistor" is the generic name given to thermally sensitive resistors. Negative temperature coefficient thermistor is generally called as thermistor. Depending on the manufacturing method and the structure, there are many shapes and characteristic for various purposes. The thermistor resistance values, unless otherwise specified, are classified at a standard temperature of 25°C. The resistance of a temperature is solely a function of its absolute temperature

Refer to datasheet of the thermistor, the mathematic expression which relates the resistance and the absolute temperature of a thermistor is shown in Equation.

$$\mathsf{R}_{1} = \mathsf{R}_{2} \times \mathsf{e}^{\beta \cdot \left(\frac{1}{\mathsf{T}_{1}}, \frac{1}{\mathsf{T}_{2}}\right)} \tag{3}$$

Where: R1 is the resistance at absolute temperature T1, R2 is the resistance at absolute temperature T2 and  $\beta$  is a constant which depends on the material of the thermistor.

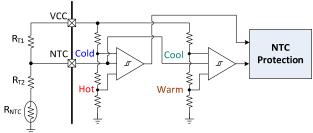

The MP2672 continuously monitors battery's temperature by measuring the voltage at the NTC pins. This voltage is determined by the resistive divider whose ratio produced by different resistance of the NTC thermistor under different ambient temperature of the battery.

MP2672 internally sets a pre-determined upper and lower bound of the range. If the voltage at the NTC pin goes out of hot/cold threshold which means the temperature is outside safe operating limit. At this time, the charging is ceased unless the operating temperature returns into the safe range.

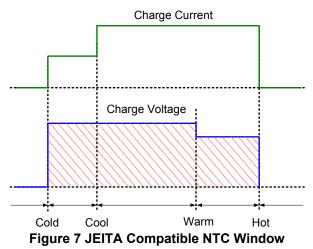

To satisfy the JEITA requirement, the MP2672 monitors four temperature threshold, the cold battery threshold (e.g.  $T_{NTC}$ <0°C), the cool battery threshold (e.g. 0°C< $T_{NTC}$ <10°C), the warm battery threshold (e.g. 45°C< $T_{NTC}$ <60°C), and the hot battery threshold (e.g.  $T_{NTC}$ <60°C). For given NTC thermistor, these temperatures correspond to the V<sub>COLD</sub>, V<sub>COOL</sub>, V<sub>WARM</sub>, and V<sub>HOT</sub>. When V<sub>NTC</sub><V<sub>HOT</sub> or V<sub>NTC</sub>>V<sub>COLD</sub>, the charging is suspended and timers are suspended.

When  $V_{HOT} < V_{NTC} < V_{WARM}$ , the battery regulation voltage  $V_{BATT\_REG}$  is reduced by 140mV from the programmable threshold.

When  $V_{\text{COOL}} < V_{\text{NTC}} < V_{\text{COLD}}$ , the charging current is reduced to half of the programmable charge current.

As Figure 8, given a thermistor is selected, two of four temperature thresholds can be programmable via changing values of  $R_{T1}$  and  $R_{T2}$ .

Figure 8 Diagram of NTC Protection Circuit

Thermal Regulation and Thermal Shutdown

To guaranteed safe operation, the MP2672 limits the die temperature to a preset value 120°C. When the internal junction temperature reaches the preset threshold, the MP2672 starts to reduce the charge current to prevent higher power dissipation. When the junction temperature reaches 150°C, the step-up converter goes into shutdown mode.

#### Indications

MP2672 has two open-drain pins ACOK and

STAT to indication the input power and charging status. The behavior is shown in table 3.

#### Table 3 Indication in Difference Cases

| Charging State                                                                                   | ACOK | STAT               |

|--------------------------------------------------------------------------------------------------|------|--------------------|

| In charging                                                                                      | Low  | Low                |

| Charging complete, charge disable                                                                | Low  | Open-<br>drain     |

| Charge Suspended due<br>to,<br>• Battery OVP,<br>• Timer Fault<br>• NTC fault<br>• Battery Float | Low  | Blinking<br>at 1Hz |

| Thermal Shutdown                                                                                 | Low  | Open-<br>drain     |

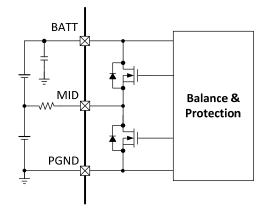

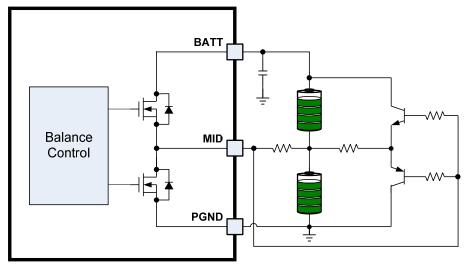

#### **Battery Cell Balance and Protection**

PRELIMINARY SPECIFICATIONS SUBJECT TO CHANGE

The MP2672 also provides the battery cell balance and protection for 2-cell application. It is able to sense the voltage across each cell, once these two cell voltages mismatch more than 50mV typically, the internal discharge path is turned on to discharge the cell of higher voltage until the two cell voltages match smaller than 30mV.

In case the battery OVP happens before the two cells are equalized, the charging will be suspended.

The MP2672 integrates the balance path and control circuit. An external power dissipation resistor is also required to limit the balance current.

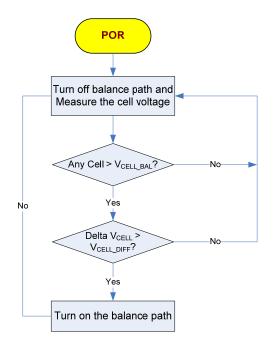

# Figure 9 Block Diagram of the Battery Balance Balancing Algorithm:

- 1. Balance block only operate in charging status.

- 2. Balance starts when any cell voltage is higher than balance start point V<sub>CELL\_BAL</sub>.

- 3. The voltage difference between cells should be higher than V<sub>CELL\_DIFF</sub>. The

MP2672 detects the cell with lower voltage in the pack, and then checks the voltage difference between each cell. If the differential voltage is higher than V<sub>CELL\_DIFF</sub>, the corresponding balance MOSFET is turned on.

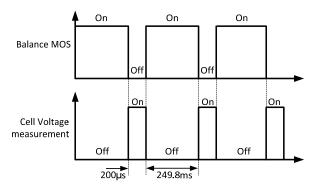

To measure the open-circuit voltage of the cell, balancing will be suspended frequently for a short duration. Charging will always operate independent of balance algorithm if no other charge fault happens.

1. Measure for 200µs, balance for 249.8ms per each 250ms cycle

Figure 10 Clock of the Battery Balance

#### Figure 11 Flow chart of the Battery Balance

For extremely unbalanced 2-cell batteries, the charger takes a few cycles to make two battery voltages balanced. For some applications, like

The MP2672 also has an option to automatically disable the termination if the cell balance is active. By doing this the two cells will be matched better when charging terminated.

Figure 12 External Cell balance circuit

#### **Series Interface**

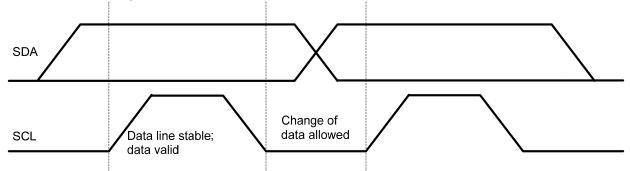

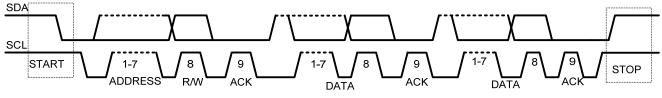

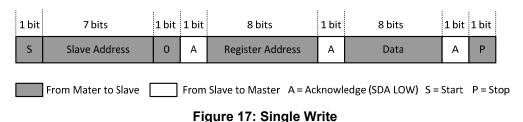

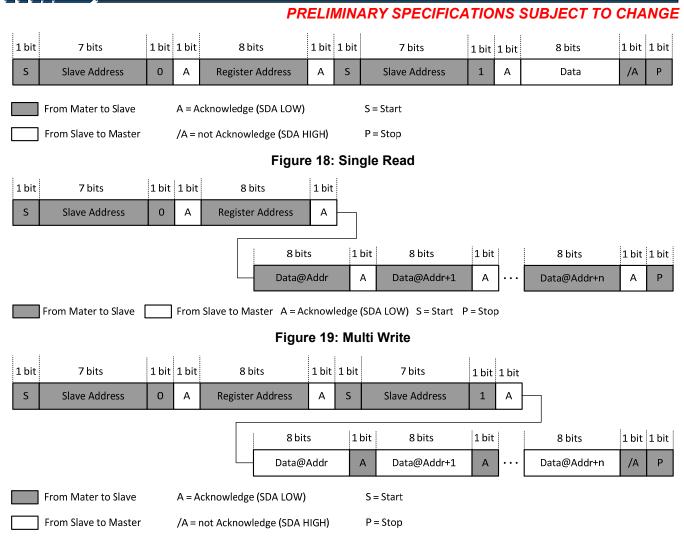

The IC uses an I<sup>2</sup>C compatible interface for flexible charging parameters setting and instantaneous device status reporting.  $I^2 \tilde{C}^{TM}$  is a bidirectional 2-wire serial interface developed by Philips Semiconductor (now NXP Semiconductors). Only two bus lines are required: a serial data line (SDA) and a serial clock line (SCL). The device can be considered a master or a slave when performing data transfers. A master is the device which initiates a data transfer on the bus and generates the clock signals to permit the transfer. At that time, any device addressed is considered as a slave.

The device operates as a slave device with the address 4BH, receiving control inputs from the

master device, like a micro controller or a digital signal processor.

The I<sup>2</sup>C interface supports both standard mode (up to 100kbits), and fast mode (up to 400kbits). Both SDA and SCL are bi-direction lines, connecting to the positive supply voltage via a current source or pull-up resistor. When the bus is free, both lines are HIGH. The SDA and SCL pins are open drain.

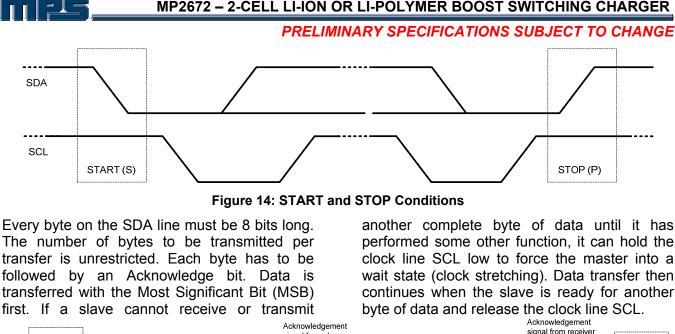

The Data on the SDA lint must be stable during the HIGH period of the clock. The HIGH or LOW state of the data line can only change when the clock signal on the SCL line is LOW. One clock pulse is generated for each data bit transferred.

All the transactions begin with a START(S) and can be terminated by a STOP (P). A HIGH to LOW transition on the SDA lint while SCI is HIGH defines a START condition. A LOW to HIGH transition on the SDA lint when the SCL is HIGH defines a STOP condition. START and STOP conditions are always generated by the master. The bus is considered busy after the START condition, and free after the STOP condition.

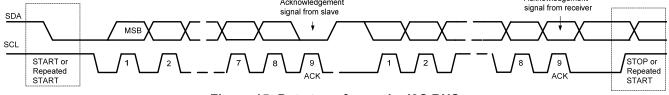

Figure 15: Data transfer on the I2C BUS

The acknowledge takes place after every byte. The acknowledge bit allows the receiver to signal the transmitter that the byte was successfully received and another byte may be sent. All clock pulses, including the acknowledge 9<sup>th</sup> clock pulse, are generated by the master.

The transmitter releases the SDA line during the acknowledge clock pulse so the receiver can pull the SDA line LOW and it remains HIGH during the 9<sup>th</sup> clock pulse, this is the Not Acknowledge signal. The master can then generate either a STOP to abort the transfer or a repeated START to start a new transfer.

After the START, a slave address is sent, this address is 7 bits long followed by the  $8^{th}$  a data direction bit (bit R/W), A zero indicates a transmission (WRITE) and a one indicates a request for data (READ). The complete data transfer is shown in Figure 15.

Figure 16: Complete Data Transfer

If the register address is not defined, the charger IC send back NACK and go back to the idle state.

MP2672 – 2-CELL LI-ION OR LI-POLYMER BOOST SWITCHING CHARGER

# I<sup>2</sup>C Register MAP IC Address 4BH

| Register<br>Name | Address | R/W | Description                                                          | Default                |

|------------------|---------|-----|----------------------------------------------------------------------|------------------------|

| REG00            | 0x00    | R/W | Battery regulation voltage, charge configure and SYS voltage setting | 0011 1000              |

| REG01            | 0x01    | R/W | Balance setting and charge current setting                           | 1000 1111              |

| REG02            | 0x02    | R/W | Timer setting                                                        | <mark>1001</mark> 0101 |

| REG03            | 0x03    | R   | Status register                                                      | 0000 0000              |

| REG04            | 0x04    | R   | Fault register                                                       | 0000 0000              |

## REG 00H (Default: 0011 1000)

| Bit | Name                      | POR | Reset by<br>REG_RST | Reset by<br>WTD | R/W                                        | Description                             | Comment                                                                              |

|-----|---------------------------|-----|---------------------|-----------------|--------------------------------------------|-----------------------------------------|--------------------------------------------------------------------------------------|

| 7   | V <sub>BATT_REG</sub> [2] | 0   | Y                   | Y               | R/W                                        | 000 – 8.3V<br>001 – 8.4V                | Battery Regulation                                                                   |

| 6   | V <sub>BATT_REG</sub> [1] | 0   | Y                   | Y               | R/W                                        | 010 – 8.5V<br>011 – 8.6V<br>100 – 8.7V  | Voltage<br>Default: (8.4V)                                                           |

| 5   | V <sub>BATT_REG</sub> [0] | 1   | Y                   | Y               | 101 – 8.8V<br>R/W 110 – 8.9V<br>111 – 9.0V |                                         | OTP Programmable.                                                                    |

| 4   | CHG CONFIG                | 1   | Y                   | Y               | R/W                                        | 0 – Charge Disable<br>1 – Charge Enable | Default: (charge<br>Enable)                                                          |

| 3   | V <sub>BATT_PRE</sub> [2] | 1   | Y                   | N               | R/W                                        | 0.4V                                    | <b>System Minimum</b><br><b>Voltage Offset</b><br>Offset: 6.0V<br>Range: 6.0V – 6.7V |

| 2   | V <sub>BATT_PRE</sub> [1] | 0   | Y                   | Ν               | R/W                                        | 0.2V                                    | Default: 6.4V<br>This threshold is also<br>used as the per-                          |

| 1   | V <sub>BATT_PRE</sub> [0] | 0   | Y                   | N               | R/W                                        | 0.1V                                    | charge battery voltage<br>threshold.<br>OTP Programmable                             |

| 0   | V <sub>TRACK</sub>        | 0   | Y                   | N               | R/W                                        | 0 – 200mV<br>1 – 300mV                  | Battery Track<br>Voltage<br>Default: 200mV                                           |

### REG 01H (Default: 1000 1111)

| Bit | Name                     | POR | Reset by<br>REG_RST | Reset by<br>WTD | R/W | Description               | Comment                                                                             |

|-----|--------------------------|-----|---------------------|-----------------|-----|---------------------------|-------------------------------------------------------------------------------------|

| 7   | NTC_TYPE                 | 1   | Y                   | Y               | R/W | 0 – Standard<br>1 – JEITA | Default: JEITA.<br>OTP programmable.                                                |

| 6   | $V_{CELL\_BAL}$          | 0   | Y                   | Y               | R/W | 0 - 3.5V<br>1 - 3.7V      | Cell Balance Start Point<br>Default: 3.5V<br>OTP programmable.                      |

| 5   | Balance<br>Threshold_H2L | 0   | Y                   | Y               | R/W | 0 - 50mV<br>1 - 70mV      | Cell Balance threshold<br>Default: 50mV<br>OTP programmable.                        |

| 4   | Balance<br>Threshold_L2H | 0   | Y                   | Y               | R/W | 0 - 50mV<br>1 - 70mV      | Cell Balance threshold<br>Default: 50mV<br>OTP programmable.                        |

| 3   | I <sub>CC</sub> [2]      | 1   | Y                   | Y               | R/W | 800mA                     | Fast Charge Current<br>Setting                                                      |

| 2   | I <sub>cc</sub> [2]      | 1   | Y                   | Y               | R/W | 400mA                     | If R <sub>ISET</sub> is 6kΩ<br>Offset: 500mA<br>Range: 500mA – 2000mA               |

| 1   | I <sub>cc</sub> [1]      | 1   | Y                   | Y               | R/W | 200mA                     | Default: 2000mA (1111)<br>If R <sub>ISET</sub> is 24kΩ                              |

| 0   | I <sub>CC</sub> [0]      | 1   | Y                   | Y               | R/W | 100mA                     | Offset: 125mA<br>Range: 125mA – 500mA<br>Default: 500mA (1111)<br>OTP programmable. |

### REG 02H (Default: 1001 0101)

| Bit | Name                               | POR | Reset by<br>REG_RST | Reset by<br>WTD | R/W                                                                                                                                     | Description                                                                       | Comment                                                           |

|-----|------------------------------------|-----|---------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|-------------------------------------------------------------------|

| 7   | FSW                                | 1   | Y                   | Y               | R/W                                                                                                                                     | 0 – 600kHz<br>1 – 1200kHz                                                         | Default: (1)1200kHz<br>OTP Programmable                           |

| 6   | I <sup>2</sup> C WD Timer<br>Reset | 0   | Y                   | Ν               | R/W                                                                                                                                     | 0 – Normal<br>1 – Reset                                                           | Default: 0 (Normal)                                               |

| 5   | WD Timer [1]                       | 0   | Y                   | Ν               | R/W         00 – Disable timer           01 – 40s         01 – 80s           R/W         10 – 80s           11 – 160s         11 – 160s |                                                                                   | I <sup>2</sup> C WD Timer Limit<br>Default: 40s (01)              |

| 4   | WD Timer [0]                       | 1   | Y                   | Ν               |                                                                                                                                         |                                                                                   | OTP programmable.                                                 |

| 3   | Register Reset                     | 0   | Y                   | Ν               | R/W                                                                                                                                     | 0 - Keep current setting<br>1 - Reset                                             | Default: 0<br>After Reset, this bit go<br>back to 0 automatically |

| 2   | CHG_TMR [1]                        | 1   | Y                   | Y               | R/W                                                                                                                                     | 00 – Disable CHG<br>Timer                                                         | Default 10 (12 hrs)                                               |

| 1   | CHG_TMR [0]                        | 0   | Y                   | Y               | R/W                                                                                                                                     | 01 – 8 hrs<br>10 – 12 hrs<br>11 – 20 hrs                                          | Default: 10 (12 hrs)                                              |

| 0   | TMRX2_EN                           | 1   | Y                   | Y               | R/W                                                                                                                                     | 0 – Disable 2x<br>extended safety timer<br>1 – Enable 2x extended<br>safety timer | Default: 1 (Enable)                                               |

## REG 03H (Default: 0000 0000)

| Bit | Name               | POR | Reset by<br>REG_RST | Reset by<br>WTD | R/W    | Description                                                      | Comment     |

|-----|--------------------|-----|---------------------|-----------------|--------|------------------------------------------------------------------|-------------|

| 7   | Reserved           | NA  | NA                  | NA              | R      | Reserved                                                         | Reserved    |

| 6   | Reserved           | NA  | NA                  | NA              | R      | Reserved                                                         | Reserved    |

| 5   | CHG_STAT [1]       | 0   | NA                  | NA              | R      | 00 – Not charge<br>01 – Pre charge<br>10 – constant-current      | Default: 00 |

| 4   | CHG_STAT [0]       | 0   | NA                  | NA              | charge |                                                                  |             |

| 3   | PPM_STAT           | 0   | NA                  | NA              | R      | 0 – Not PPM<br>1 – VINPPM                                        | Default: 0  |

| 2   | BATTFLOAT_S<br>TAT | 0   | NA                  | NA              | R      | 0 – Battery present<br>1 – Battery missing                       | Default: 0  |

| 1   | THERM_STAT         | 0   | NA                  | NA              | R      | 0 – Normal<br>1 – Thermal regulation                             | Default: 0  |

| 0   | VSYS_STAT          | 0   | NA                  | NA              | R      | 0 – Not in VSYSMIN<br>regulation<br>1 – In VSYSMIN<br>regulation | Default: 0  |

#### REG 04H (Default: 0000 0000)

| Bit | Name              | POR | Reset by<br>REG_RST | Reset by<br>WTD | R/W | Description                                  | Comment      |

|-----|-------------------|-----|---------------------|-----------------|-----|----------------------------------------------|--------------|

| 7   | WD_FAULT          | 0   | NA                  | NA              | R   | 0 - Normal<br>1 - WD Timer<br>Expiration     | Default: 0   |

| 6   | INPUT_FAULT       | 0   | NA                  | NA              | R   | 0 - Normal<br>1 - Input fault (OVP)          | Default: 0   |

| 5   | THERM<br>SD_FAULT | 0   | NA                  | NA              | R   | 0 – Normal<br>1 – Thermal shutdown           | Default: 0   |

| 4   | TIMER_FAULT       | 0   | NA                  | NA              | R   | 0 – Normal<br>1 – Safety timer<br>expiration | Default: 0   |

| 3   | BAT_FAULT         | 0   | NA                  | NA              | R   | 0 – Normal,<br>1 – Battery OVP,              | Default: 0   |

| 2   | NTC_FAULT [2]     | 0   | NA                  | NA              | R   | 000 – Normal                                 |              |

| 1   | NTC_FAULT [1]     | 0   | NA                  | NA              | R   | 001 – NTC cold<br>010 – NTC cool             | Default: 000 |

| 0   | NTC_FAULT [0]     | 0   | NA                  | NA              | R   | 011 – NTC warm<br>100 – NTC hot              |              |

## **REG 05H (Default: 1110 0000)**<sup>(6)</sup>

| Bit         | Name                   | POR | Reset by<br>REG_RST | Reset by<br>WTD | Description |                                                                                                                                                                                                                                                    | Comment    |

|-------------|------------------------|-----|---------------------|-----------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

| 7           | RCHG                   | 1   | NA                  | NA              | NA          | $\begin{array}{l} 0 - \text{No charging after input power} \\ \text{on when } V_{\text{BATT}} > V_{\text{RECH}}. \end{array} \\ 1 - \text{Automatic charging after input} \\ \text{power on when } V_{\text{BATT}} > V_{\text{RECH}}. \end{array}$ | Default: 1 |

| 6           | Reserved               | NA  | NA                  | NA NA Reserved  |             |                                                                                                                                                                                                                                                    |            |

| 5           | BALANCE_EO<br>C_EN     | 1   | NA                  | NA              | NA          | <ul> <li>0 – Not Suspend termination</li> <li>when cell balance is active</li> <li>1 – Suspend termination when</li> <li>cell balance is active</li> </ul>                                                                                         | Default: 1 |

| 4           | T <sub>J_REG</sub> [1] | 0   | NA                  | NA              | NA          | 00 - 120°C<br>01 - 100°C                                                                                                                                                                                                                           | Default:00 |

| 3           | T <sub>J_REG</sub> [0] | 0   | NA                  | NA              | NA          | 10 - 80°C<br>11 - 60°C                                                                                                                                                                                                                             | Default:00 |

| 2           | Reserved               | NA  | NA                  | NA              | NA          | Reserved                                                                                                                                                                                                                                           | Reserved   |

| 1           | Reserved               | NA  | NA                  | NA              | NA          | Reserved                                                                                                                                                                                                                                           | Reserved   |

| 0<br>Notes: | Reserved               | NA  | NA                  | NA              | NA          | Reserved                                                                                                                                                                                                                                           | Reserved   |

Notes:

6) This register is for OTP only and not accessible to customers.

## **OTP MAP**

| #   | Bit7              | Bit6            | Bit5                    | Bit4                    | Bit3                                                               | Bit2                              | Bit1 | Bit0 |  |

|-----|-------------------|-----------------|-------------------------|-------------------------|--------------------------------------------------------------------|-----------------------------------|------|------|--|

| 00  | V <sub>BA</sub> - | rt_reg: 8.3V-9  | 9.0V                    | N/A                     | V <sub>BA</sub>                                                    | V <sub>BATT_PRE</sub> : 6.0V-6.7V |      |      |  |

| 01  | NTC Type          | $V_{CELL\_BAL}$ | V <sub>CELL_DIFF_</sub> | V <sub>CELL_DIFF_</sub> | I <sub>CC</sub> : 500mA-2000mA/100mA step (R <sub>ISET</sub> =6kΩ) |                                   |      |      |  |

| 02  | FSW               | N/A             | WATC                    | HDOG                    | N/A                                                                | N/A                               | N/A  | N/A  |  |

| 05* | RCHG              | N/A             | BALANCE<br>_EOC_EN      |                         | <sub>REG</sub> :<br>)0/120⁰C                                       | N/A                               | N/A  | N/A  |  |

\*Note: REG05 is for OTP only, cannot be accessible to customer.

## **OTP DEFAULT**

| OTP Items                    | Default                                                                               |

|------------------------------|---------------------------------------------------------------------------------------|

| VBATT_REG                    | 8.4V                                                                                  |

| VBATT PRE                    | 6.4V                                                                                  |

| NTC Type                     | JEITA                                                                                 |

| V <sub>CELL_BAL</sub>        | 3.5V                                                                                  |

| Balance Threshold H2L        | 50mV                                                                                  |

| Balance Threshold L2H        | 50mV                                                                                  |

| I <sub>cc</sub>              | 2000mA                                                                                |

| SW FREQ                      | 1200kHz                                                                               |

| WATCHDOG                     | 40s                                                                                   |

| RCHG                         | New charge cycle starts when $V_{BATT}$ > $V_{RECH}$ after power on.                  |

| BALANCE_EOC_EN               | Enable (if two cell is not balanced, EOC is not asserted even all conditions are met) |

| Thermal Regulation Threshold | 120°C                                                                                 |

## **APPLICATION INFORMATION**

# Setting the Charge Current in Standalone Mode

In standalone mode, the charge current of the MP2672 can be set by an external resistor ( $R_{ISET}$ ) in according to Equation (4):

$$I_{\rm CC} = \frac{12k\Omega}{R_{\rm ISET}}(A)$$

(4)

The charge current can be programmed up to 2.0A. The expected  $R_{ISET}$  for a typical charge current is shown in Table 4.

| R <sub>ISET</sub> (kΩ) | I <sub>cc</sub> (A) |

|------------------------|---------------------|

| 24                     | 0.5                 |

| 12                     | 1                   |

| 6                      | 2.0                 |

In host-control mode, the  $R_{ISET}$  determines the full-scale current when  $I_{CC}$  [3:0] is set to all 1.

#### Setting the Input Minimum Voltage Limit

In charge mode, connect a resistor divider from IN to AGND tapped to VLIM to program the input minimum voltage using Equation (5):

$$V_{\text{IN}_{\text{MIN}}} = 1.2 \text{V} \times \frac{\text{R}_{\text{H}} + \text{R}_{\text{L}}}{\text{R}_{\text{L}}}$$

(5)

Where 1.2V is the reference of the input minimum voltage loop. With given  $R_L$ ,  $R_H$  can be calculated as below,

$$\mathsf{R}_{\mathsf{H}} = \mathsf{R}_{\mathsf{L}} \times \frac{\mathsf{V}_{\mathsf{IN}\_\mathsf{MIN}} - 1.2\mathsf{V}}{1.2\mathsf{V}} \tag{6}$$

For example, assume 4.675V input minimum voltage limit is expected,  $R_L$ =10k $\Omega$  and  $R_H$ =27.4k $\Omega$  would be one of the choices.

#### **Resistor Selection for the NTC Sensor**

Figure 6 shows an internal resistor divider reference circuit that limits both the high and low temperature thresholds at V<sub>HOT</sub> and V<sub>COLD</sub> respectively. For a given NTC thermistor, select appropriate R<sub>T1</sub> and R<sub>T2</sub> to set the NTC window.  $R_{ro} = \frac{R_{NTC\_HOT} \bullet V_{COLD} \bullet (1-V_{HOT}) - R_{NTC\_COLD} \bullet V_{HOT} \bullet (1-V_{COLD})}{R_{ro} = R_{NTC\_HOT} \bullet V_{COLD} \bullet (1-V_{HOT}) - R_{NTC\_COLD} \bullet V_{HOT} \bullet (1-V_{COLD})}$

$$V_{HOT}$$

-  $V_{COLD}$

$$R_{T1} = \frac{(1 - V_{COLD}) \times (R_{NTC_{COLD}} + R_{T2})}{V_{COLD}}$$

(8)

$R_{\text{NTC}_{HOT}}$  is the value of the NTC resistor at high temperature of the required temperature operation range, and  $R_{\text{NTC}_{COLD}}$  is the value of the NTC resistor at low temperature.

Figure 21 NTC Protection Block

$R_{T1}$  and  $R_{T2}$  allow the high temperature limit and low temperature limit to be programmed independently.

With this feature, the MP2672 can fit most type of NTC resistor and different temperature operation range requirements.

$R_{T1}$  and  $R_{T2}$  values depend on the type of the NTC resistor.

For example, for the 103AT thermistor, it has the following electrical characteristic:

At 0°C,  $R_{NTC_{COLD}} = 27.28 k\Omega$ ;

At 60°C,  $R_{NTC_HOT} = 3.02 k\Omega$ .

According to the above equations (7) and (8),  $V_{HOT}$  and  $V_{COLD}$  from the EC table to calculate  $R_{T1}$ =12.78k $\Omega$  and  $R_{T2}$ =3.71k $\Omega$ .

Please apply spreadsheet about  $R_{T1}$  and  $R_{T2}$  calculation if required.

www.MonolithicPower.com

4/17/2018MPS Proprietary Information. Patent Protected. Unauthorized Photocopy and Duplication Prohibited.Preliminary Specifications Subject to Change© 2018 MPS. All Rights Reserved.

(7)

#### Selecting the Inductor

Inductor selection is a trade-off between cost, size and efficiency. A lower inductance value results in lower DCR for same component size, but results in higher current ripple, higher magnetic hysteretic losses, and higher output capacitances. From a practical standpoint, the inductor ripple current does not exceed 30% of maximum input current under worst case conditions.

Choose an inductor that does not saturate under the worst-case load condition. The saturate current of inductor should be higher than peak current limit of low-side FET.

When the MP2672 works in charge mode, estimate the required inductance with Equation (9), Equation (10) and Equation (11):

$$L = \frac{V_{IN} \bullet (V_{SYS} - V_{IN})}{V_{SYS} \bullet F_{SW} \bullet \Delta I_{L_{MAX}}}$$

(9)

$$\Delta I_{L_MAX} = 2 \times \left( I_{L_PK} - I_{IN(MAX)} \right)$$

(10)